针对工业及医疗等应用的安森美半导体CMOS图像传感器方案中心议题:安森美(ON)提供的标准CMOS图像传感器方案 安森美提供的定制CMOS图像传感器方案

近年来,随着CMOS工艺技术的不断改进,CMOS传感器的应用范围也越来越广泛,包括数码相机、电脑摄像头、视频电话、手机、视频会议、智能型安保系统、汽车倒车视像雷达、玩具,以及工业、医疗等应有尽有。实际上,CMOS图像传感器最初应用于工业图像处理;在那些旨在提高生产率、质量和生产工艺经济性的全新自动化解决方案中,它至今仍然是至关重要的图像解决方案。

安森美半导体的标准及定制CMOS图像传感器方案

随着应用要求的不断提升,CMOS传感器的成像质量也在不断提高,安森美半导体利用其在这一领域的专利技术和丰富的经验,以创新的设计,采用标准CMOS工艺技术开发出了高性能CMOS有源像素传感器等多种产品。

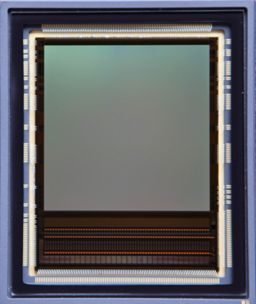

过去15年来,安森美半导体一直在为数百万像素数码摄影、达晶圆级的大面积传感器、超高速传感器、机器视觉成像、线性和二维条码成像、医用X射线成像、单芯片一体化摄像机,以及太空和核应用的抗辐射CMOS图像传感器提供行之有效的解决方案。

1) 标准图像传感器

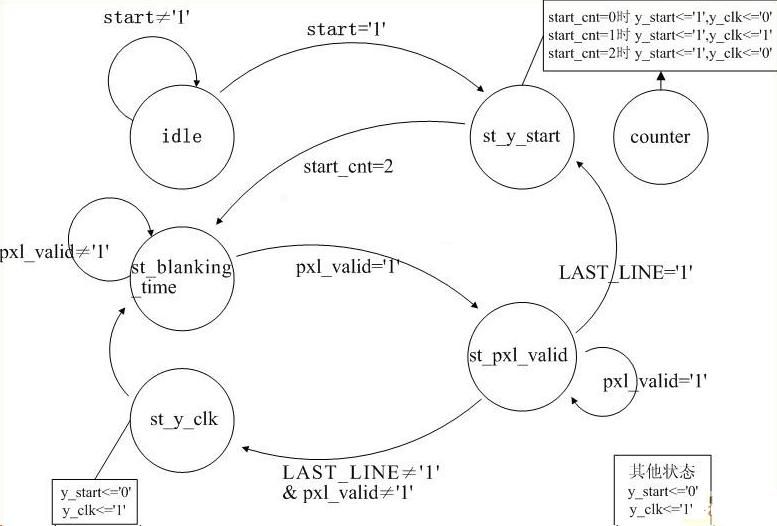

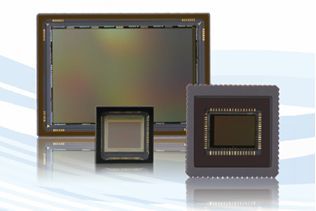

新兴应用需求的不断增长为精心设计的CMOS图像传感器带来了众多商机。除此高端机器视觉应用,二维(2D)条形码阅读器、高端保安摄像方案以及新兴的智能交通管理系统(ITS)的市场也在迅速扩大。安森美半导体新的VITA系列能满足这些新市场的需求。VITA提供可配置性、灵活性和操作方便性。

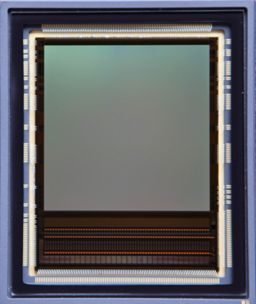

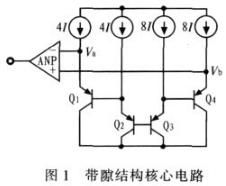

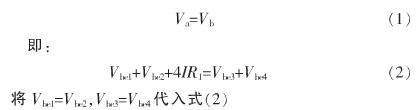

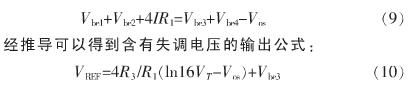

图1、VITA25K 2,500万像素、53 fps全局快门CMOS图像传感器示例

VITA系列CMOS图像传感器采用可配置操作模式,易于操作,提供带双斜率读数的流水线型和触发式全局快门、带相关双采样(CDS)的滚动快门、LVDS或CMOS输出、10位或8位精度、多个并行窗口读数等特性。应用范围包括机器视觉、条形码、智能交通管理系统(ITS)和运动监测(motion monitoring)。

安森美半导体的另一个标准图像传感器系列是LUPA。该系列是高速CMOS图像传感器的深入研发和丰富经验的结晶。LUPA器件提供的分辨率高达2048 × 2048,帧速率最高达500 fps。这些器件的功耗低至150 mW,完全没有光晕(Blooming)或滞后,为高度可靠、高灵敏度图像传感器创建了一个完善的基础。LUPA系列包含LUPA 300、LUPA 1300-2、LUPA 3000和LUPA 4000。

LUPA实现了前所未有的灵敏度,具有百万像素系列图像传感器的分辨率,其它特性包括低功耗、无光晕或图像滞后、采用流水线式全局快门,可广泛应用于高速机器视觉、工业成像、医疗成像、国防和运动分析等领域。

另外一个CMOS标准图像传感器的系列是IBIS,包括IBIS4和IBIS5图像传感器。IBIS4图像传感器的特点是图像质量高、三晶体管(3T)像素、滚动快门、高填充因数和用来提高动态范围的双斜率读数。IBIS5 CMOS图像传感器进过优化,是专门为机器视觉相机而开发的。

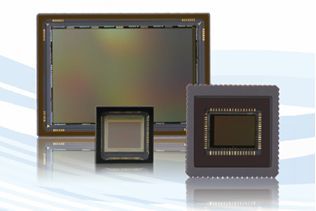

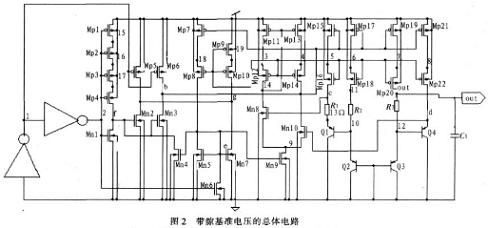

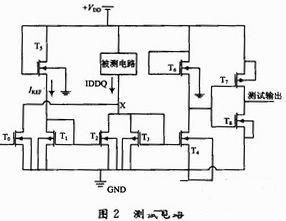

图2、IBIS系列图像传感器

IBIS4的像素分辨率高达1,400万,图像质量高,具有滚动快门和灵活的窗口和多斜率功能;IBIS5采用触发式全局快门,操作模式灵活,具有灵活的窗口和多斜率功能。它们的应用包括机器视觉、生物测量和文档扫描等。

安森美半导体标准系列的STAR图像传感器系列,是开发抗辐射CMOS像素和读出电子产品过程中广泛研究和辐照实验的成果。这些结构的总辐照剂量高达300 krad。抗辐射CMOS图像传感器可以在辐射环境下发挥重要的作用,而普通CMOS或CCD成像无法做到这一点,而使用CRT显像管又太昂贵、过重或体积过大。STAR系列包括三个产品:STAR 250、STAR 1000和HAS2,每个产品都有自己独到的优势。

总体上讲,STAR高达100万像素分辨率,具有高抗辐射、高灵敏度、低噪声的优势;可以应用在太空科学、核检验、星跟踪器和太阳传感器等方面。

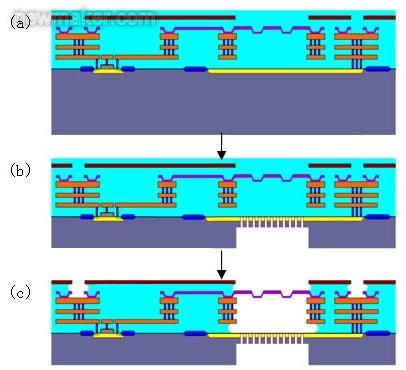

2) 定制图像传感器

安森美半导体还提供定制和针对特定应用的CMOS图像传感器,通过开发具有最先进性能的产品,帮助合作伙伴领先于竞争对手。定制设计可根据内部开发的参数功能块或采用全新的方法实现前所未有的性能和功能。

安森美半导体的专利设计和制造技术有助于优化关键参数,并与客户的应用实现完美契合。像素的大小、形状和速度、饱和度和噪声水平、动态范围和灵敏度、输出和帧速率都可以根据每个客户的需求来设定。

定制解决方案充分考虑了规格的灵活性,可实现最终应用的关键差别化,保证整个产品寿命期的有效性;高层次的架构和操作灵活性可以提高性能。定制方案的应用包括高分辨率摄影、高速成像、条形码阅读、机器视觉、医疗成像,尤其是需要低功耗、智能传感或抗辐射的阵列或线性传感器解决方案的任何应用。

安森美半导体为客户提供的典型自定义设计周期流程是客户提出最初需求,然后由安森美半导体提出建议,再经过预先研究、产品定义、产品设计、产品设计审查、原型制造、装配和功能测试、原型、性能表征、性能表征报告等过程,最后做出生产规划和生产计划,进行预生产和投产。

总结

安森美半导体提供对多重终端市场的完整的一维和二维CMOS图像传感器产品,其中既有系列标准图像传感器,也有定制及专用产品。标准系列包括最高像素2,500万、提供10位或8位精度的VITA系列,能以数百万像素分辨率提供最高500 fps帧速率的LUPA系列,提供最高1,400万像素分辨率及高图像质量的IBIS系列,以及抗辐射及提供高灵敏度的STAR系列。此外,安森美半导体为客户提供定制及专用CMOS图像传感器,帮助客户以独特产品及一流性能领先竞争对手。今后,数百万像素数码摄影及电影摄影、机器视觉、线性及二维条形码成像、工业及医疗成像、生物测定及计算及军事/航空市场将会有更多应用采用安森美半导体的图像传感器。